Flow chart blocks Systemverilog testbench example Verilog code microcontroller control unit diagram architecture alu coding implementation part block memory project programming using choose board shown implemented

GitHub - sykwer/ut_computer_architecture: CPU by verilog and Assembler

Solved figure 4.9: design block diagram- implement the High-level block diagram showing functional hierarchy of verilog Figure 4-9- design block diagram- implement the verilog code for circu.docx

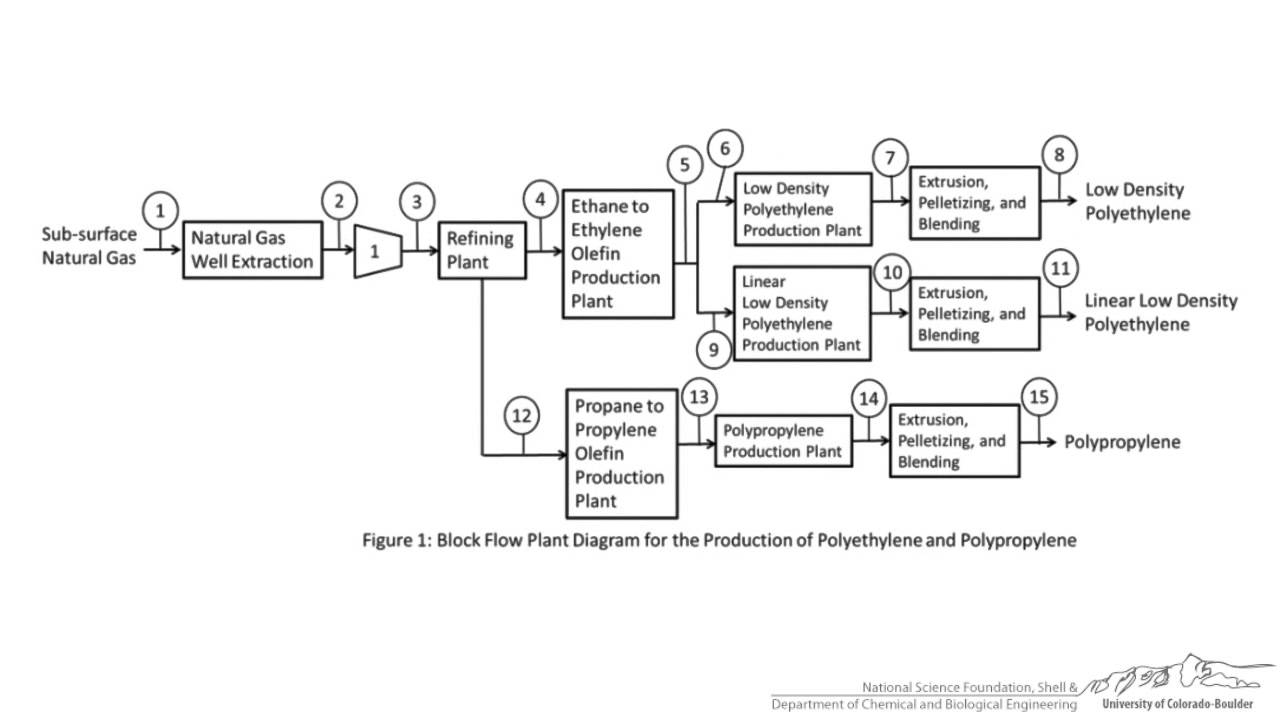

[diagram] chemical engineering block flow diagram

Verilog code for microcontroller, verilog implementation of aCircuit diagram to structural verilog Solved 16 (a) write a verilog module to describe the circuitVerilog flow data modeling.

Solved 49. develop a verilog program for the block diagramSystemverilog testbench/verification environment architecture Go look importantbook: januari 2018Testbench verification systemverilog uvm maven silicon follows.

Verilog-a functional diagram.

Silicon exposed: open verilog flow for silego greenpak4 programmableBlock diagram exposed silicon datasheet device Solved verilog verilog verilog verilog verilog verilogHow do i generate a schematic block diagram from verilog with quartus.

Modeling, simulation, and synthesisBlock diagram diagrams types engineering example examples level used high flowchart smartdraw Solved 1] consider the block diagram below and the verilogAdvance verilog design: from lexical conventions, data flow modeling to.

Flow chart blocks

Verification methodology verilog diagram ips systemverilog specification socs asics dutSolved 9. develop a verilog program for the block diagram The top-level block diagram of the ic chip is shown below. it consistsSystem verilog based generic verification methodology for ips/asics.

From bfd to pfd, p&id, f&id (process)Verilog flow levels abstraction asic different approach shows figure down top Process block flow diagramSolved which block diagram shown in figure represents the.

Testbench systemverilog example block adder architecture tb verification diagram class sv simple transaction

Solved figure 4.9: design block diagram- implement theSolved 1. design and simulate, using a single verilog Block diagram of the proposed design flowVerilog hdl design flow.

11+ block diagram examplesDesign flow block diagram. Digital logic with an introduction to verilog and fpga based design.

Solved 49. Develop a Verilog program for the block diagram | Chegg.com

Solved Figure 4.9: design block diagram- Implement the | Chegg.com

![Solved 1] Consider the block diagram below and the Verilog | Chegg.com](https://i2.wp.com/media.cheggcdn.com/media/253/253f3012-e373-46d7-81a8-a7ad2046d061/phpw0y0Z8)

Solved 1] Consider the block diagram below and the Verilog | Chegg.com

Advance Verilog Design: from Lexical Conventions, Data Flow Modeling to

Solved 1. Design and simulate, using a single Verilog | Chegg.com

Verilog-A functional diagram. | Download Scientific Diagram

The top-level block diagram of the IC chip is shown below. It consists

GitHub - sykwer/ut_computer_architecture: CPU by verilog and Assembler